# Wire Length Distribution Model Considering Core Utilization for SoC

Takanori Kyogoku\*, Junpei Inoue, Takumi Uezono, Hidenari Nakashima, Kenichi Okada, and Kazuya Masu

Precision and Intelligence Laboratory, Tokyo Institute of Technology, Japan

\* kyogoku@lsi.pi.titech.ac.jp

## 1. Background

In recent years, a lot of system LSIs are designed.

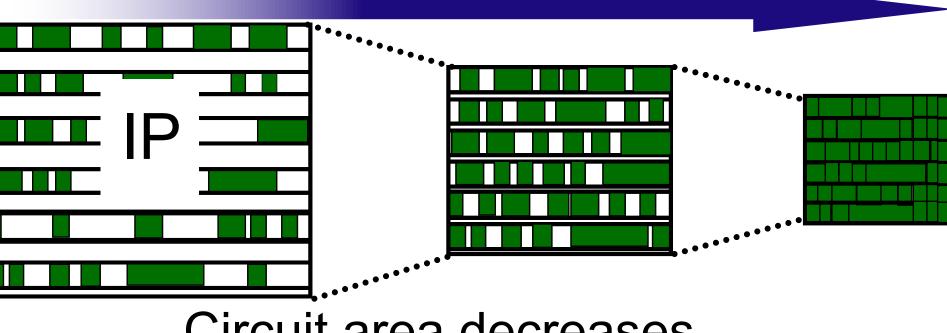

LSI design based on IP (Intellectual Properties)

Development of circuit as a component of a SoC (System on a Chip).

1. Manufacturing cost is reduced. 2. Design time is reduced.

MPU DRAM

Deciding area allocation of IP is important.

#### How to change circuit area of IP...

Core Utilization increases...

Circuit area decreases.

RC interconnect delay changes.  $\rightarrow$

Circuit area has large impact on performance<sup>[2]</sup>

In the recent technology, interconnect delay determines the circuit performance.

#### Trade-Off

| Core Utilization         | low                    | high                   |

|--------------------------|------------------------|------------------------|

| Interconnect Length      | long                   | short                  |

| (Resistance/Capacitance) | ( <mark>large</mark> ) | ( <mark>small</mark> ) |

| Interconnect Density     | low                    | high                   |

| (Capacitance)            | ( <mark>small</mark> ) | ( <mark>large</mark> ) |

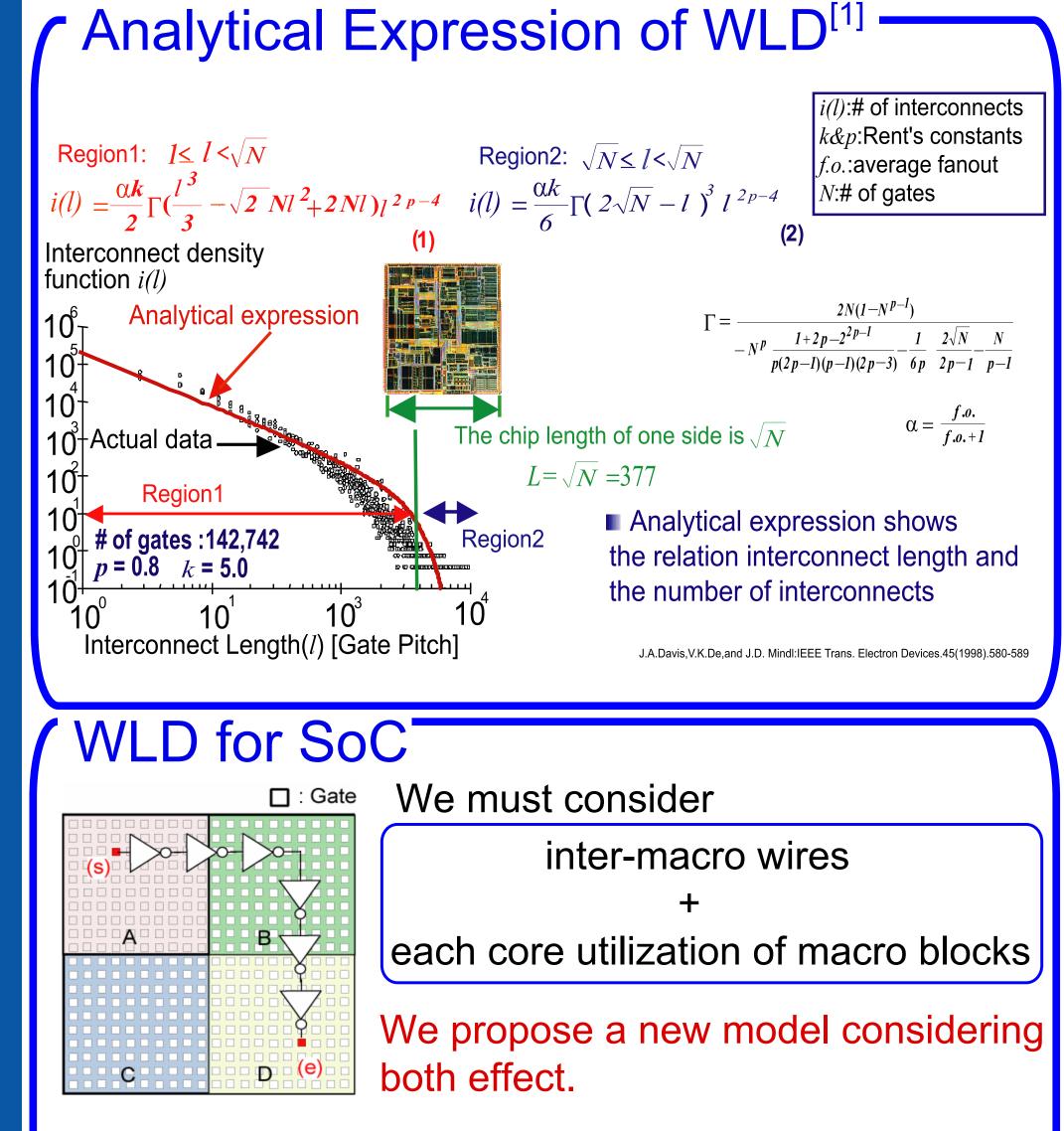

We use Wire Length Distribution model to estimate resistance and capacitance.

## 2. Wire Length Distribution Model (WLD)

### WLD model of each macro blocks<sup>[2]</sup>

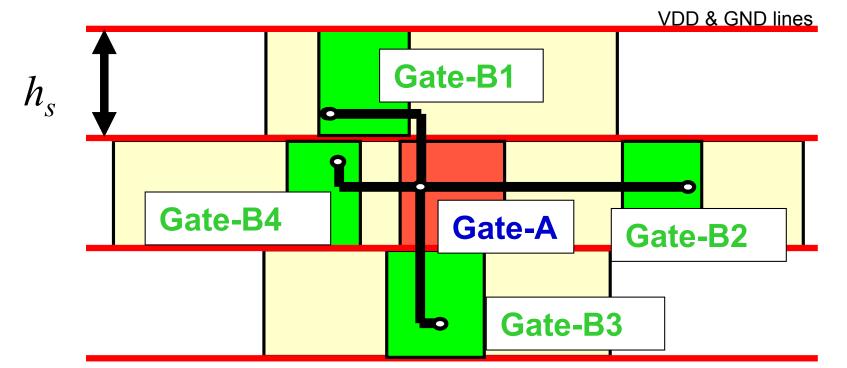

Gate is arranged in random size and position.

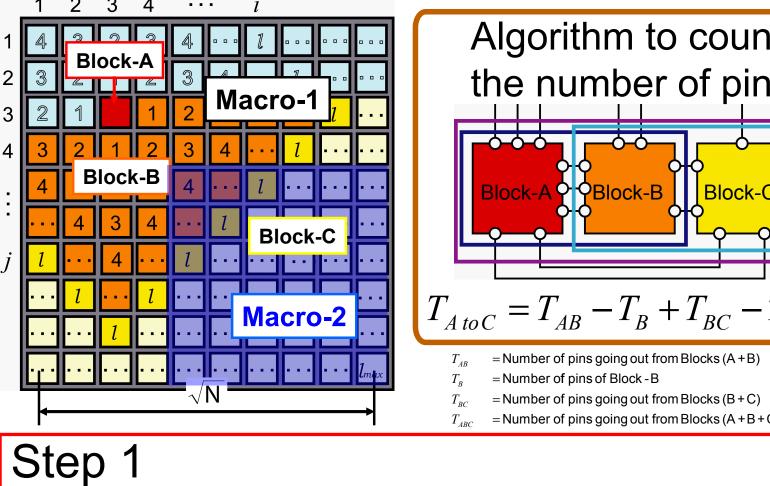

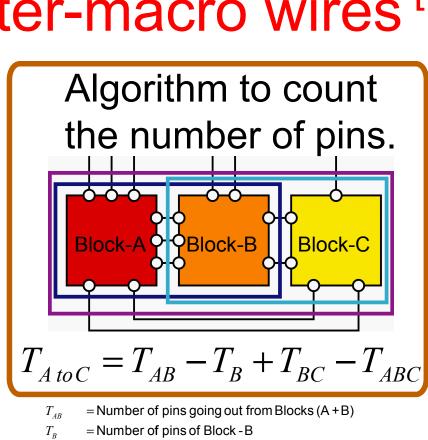

### WLD model of inter-macro wires <sup>[3]</sup>

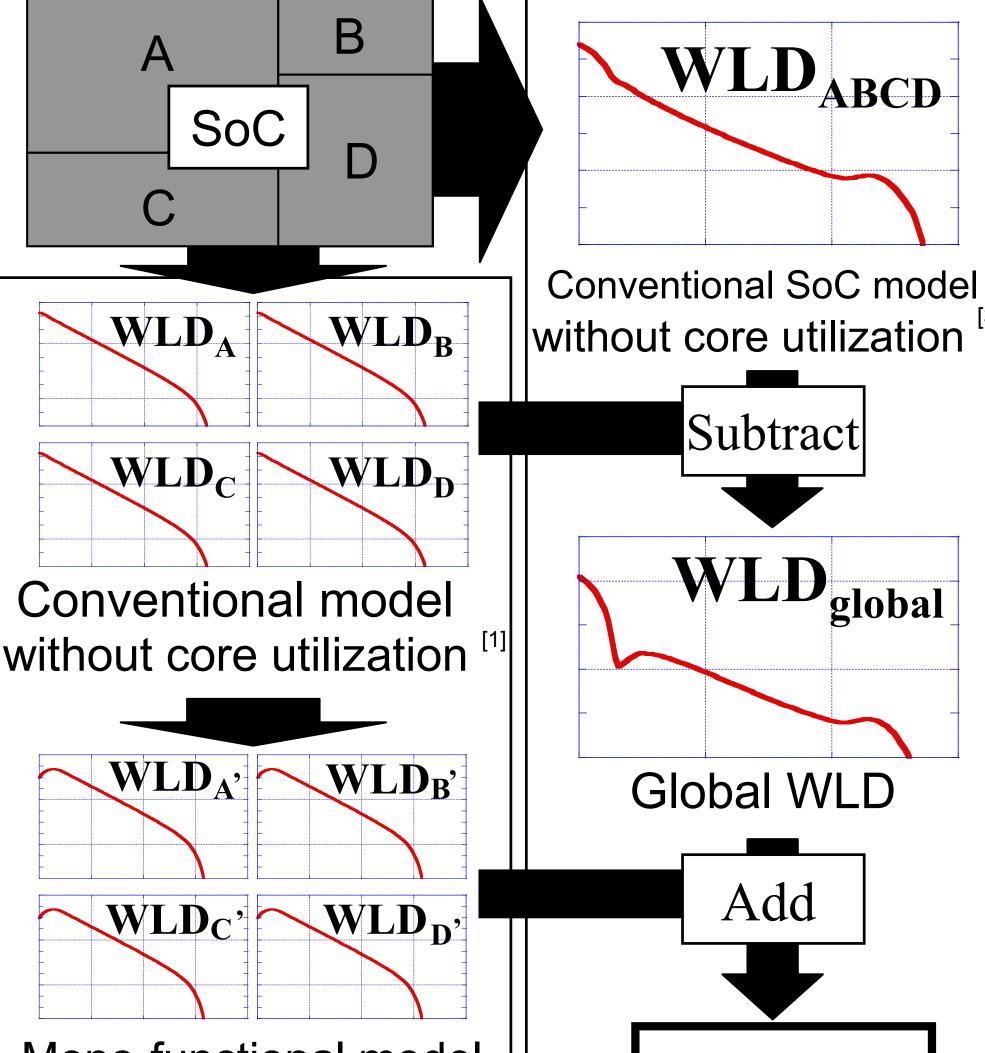

### The derivation flow of proposed WLD model

#### Assumption

- Global layer is used to connect macro blocks

- Gate size of repeaters is optimized\*.

\* H. B. Bakoglu et. al., "Circuits, Interconnections, and Packaging for VLSI", (1990)

Block-C has the distance  $\ell$  from Block-A. Block-B has the distance less than  $\ell$ . Step 2

Count the number of I/O pins connecting Block-A to Block-C (*T*AtoC). Step 3 Apply Step1,2 to all the gates of a circuit

| Mono-functional model<br>with core utilization <sup>[2]</sup> | WLD <sub>total</sub> |  |  |

|---------------------------------------------------------------|----------------------|--|--|

| Inside macro blocks                                           | total WLD            |  |  |

| [1] J.Davis et. al., IEEE Trans. on ED 45-3 (1998) 580        |                      |  |  |

| [2] H.Nakashima et.al., Proc. IEEE DATE 2(2004) 1210          |                      |  |  |

| [3] T.Kyogoku <i>et., al., Proc. SASIMI</i> (2005) 176        |                      |  |  |

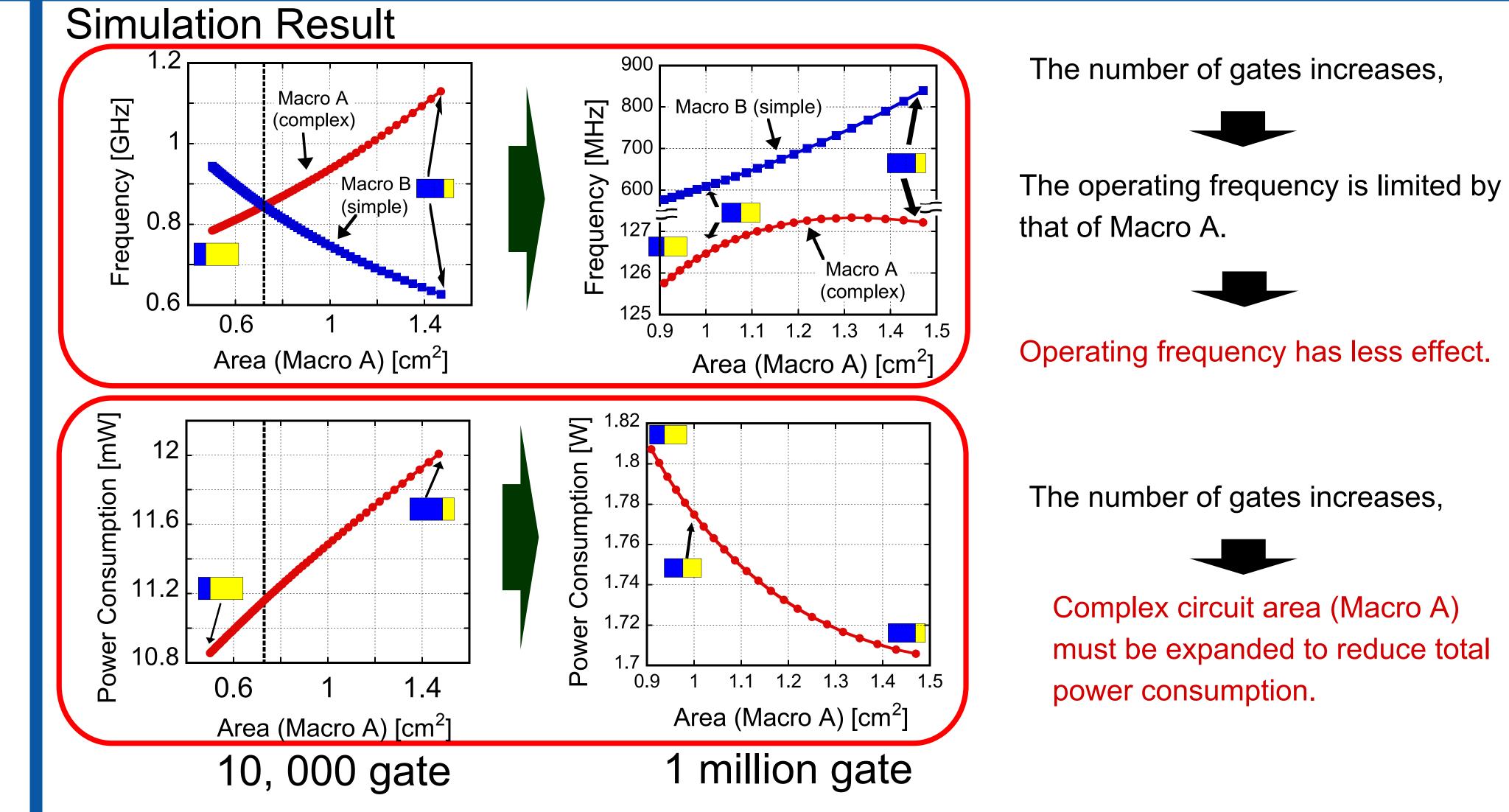

### **3.** Results

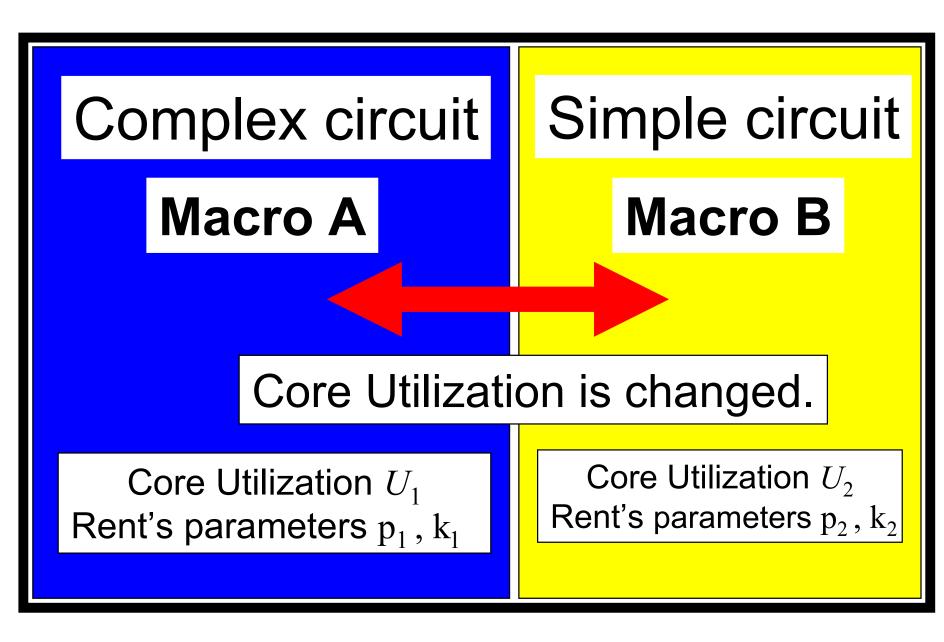

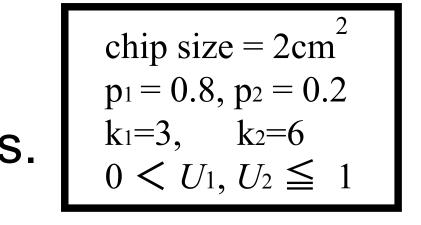

### Chip model

These macros have the same number of gate. Chip has 2 macro blocks. Total chip area is fixed.

- Area of complex circuit is changed.

- Area of Macro B is decided automatically.

Complex circuit area (Macro A) must be expanded to reduce total

Area of macro block must be large as long as operating frequency is not violated.

## 4. Conclusion

Area allocation of macro blocks inside SoC is important.

>>> The area of circuit which have large number of gate must be expanded to reduce power consumption. Future work --- To consider the influence of VIA and to simulate real cell placement.