# A Loss Optimization Method Using WD Product for On-Chip Differential Transmission Line Design

Hiroyuki Ito, Kenichi Okada, and Kazuya Masu Integrated Research Institute, Tokyo Institute of Technology

# Background

Miniaturization of Si CMOS process

- Cut-off frequency of the NMOS transistor is projected to become 300 GHz at 45 nm technology node in 2010.

- = Clock frequency of digital circuit will reach 15 GHz.

- RF CMOS circuits that can operate at over 10 GHz are reported.

On-chip transmission lines have been becoming increasingly important for high-speed digital and RF circuits.

# Problems in transmission line design specific to Si LSI

- Dielectric loss in Si substrate

- Large resistive loss due to the skin effect and the eddy current in Si substrate

# Why WD product?

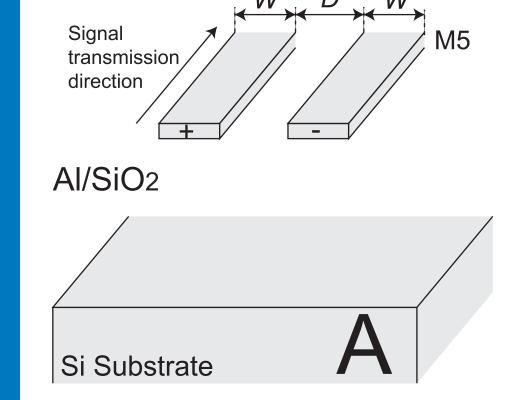

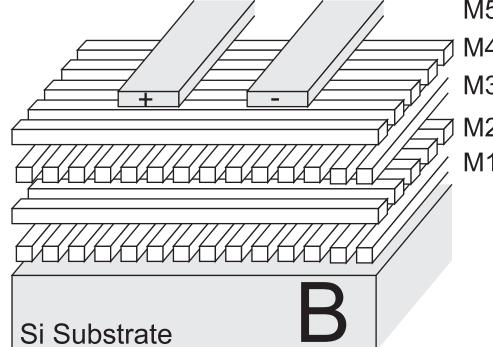

W: Line width, D: Distance between lines The WD product can give the attenuation characteristics of the transmission line.

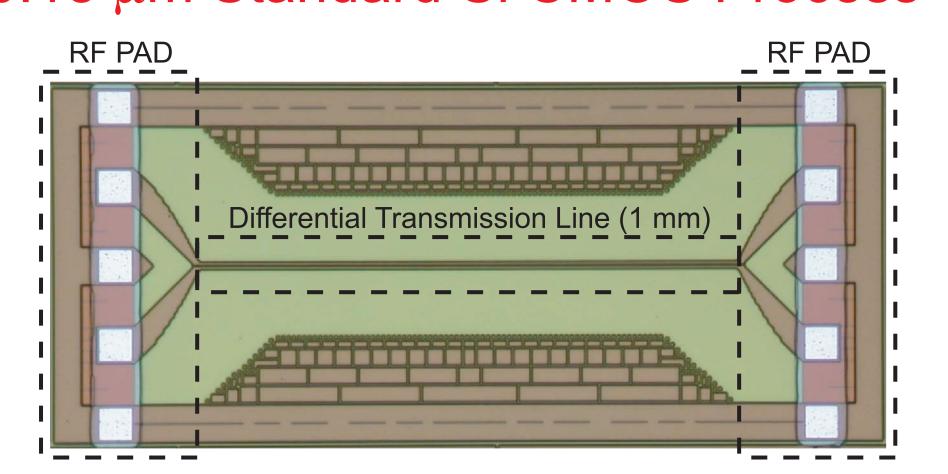

## Structures of DUTs

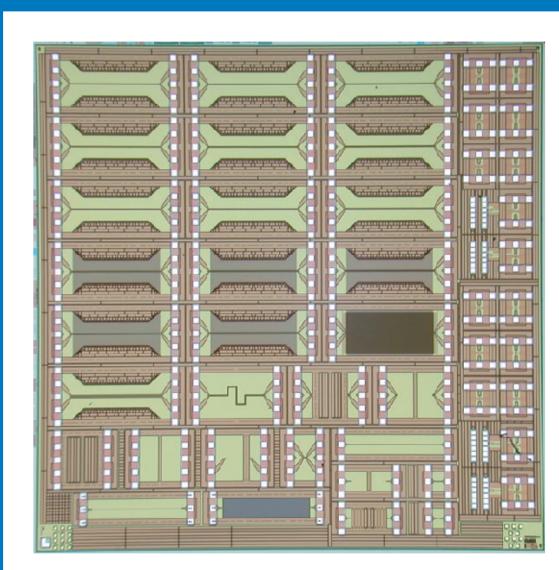

#### 0.18 μm Standard Si CMOS Process

| VV          | D           | WD    | Lossless Zdiff | Type |

|-------------|-------------|-------|----------------|------|

| 2.0 μm      | 1.8 μm      | 3.6   | 80 Ω           | Α    |

| 2.0 μm      | 2.9 μm      | 5.8   | 100 Ω          | Α    |

| 2.0 μm      | 4.3 μm      | 8.6   | 120 Ω          | Α    |

| 4.0 μm      | 2.3 μm      | 9.2   | 80 Ω           | Α    |

| $4.0~\mu m$ | $3.7~\mu m$ | 14.8  | 100 Ω          | Α    |

| 4.0 μm      | 5.8 μm      | 23.2  | 120 Ω          | А    |

| 6.0 μm      | 2.6 μm      | 15.6  | 80 Ω           | Α    |

| 6.0 μm      | 4.6 μm      | 27.6  | 100 Ω          | А    |

| 6.0 μm      | 7.4 μm      | 44.4  | 120 Ω          | А    |

| 10.0 μm     | 11.0 μm     | 110.0 | 120 Ω          | А    |

| 4.0 μm      | 2.3 μm      | 9.2   | 80 Ω           | В    |

| 4.0 μm      | 3.7 μm      | 14.8  | 100 Ω          | В    |

| 4.0 μm      | 5.8 μm      | 23.2  | 120 Ω          | В    |

| 2.0 μm      | 2.9 μm      | 5.8   | 100 Ω          | В    |

| 6.0 μm      | 4.6 μm      | 27.6  | 100 Ω          | В    |

- Thicknesses of metal and dielectric layers: ≈1 μm

- A line length of the differential transmission line (DTL): 1 mm

- Type A: DTL (M5)

- Type B: DTL (M5) with underlying metals (M1, M2, M3 and M4) L&S of M1, M2, M3 and M4 are 1.0 μm.

## Measurement system

- Vector network analyzer (Agilent, E8364B & N4421B)

- GSGSG type RF probes (Cascade, Infinity)

- SOLT calibration using impedance standard substrate of Cascade

- Pad de-embedding: Open and short patterns

# Characteristics

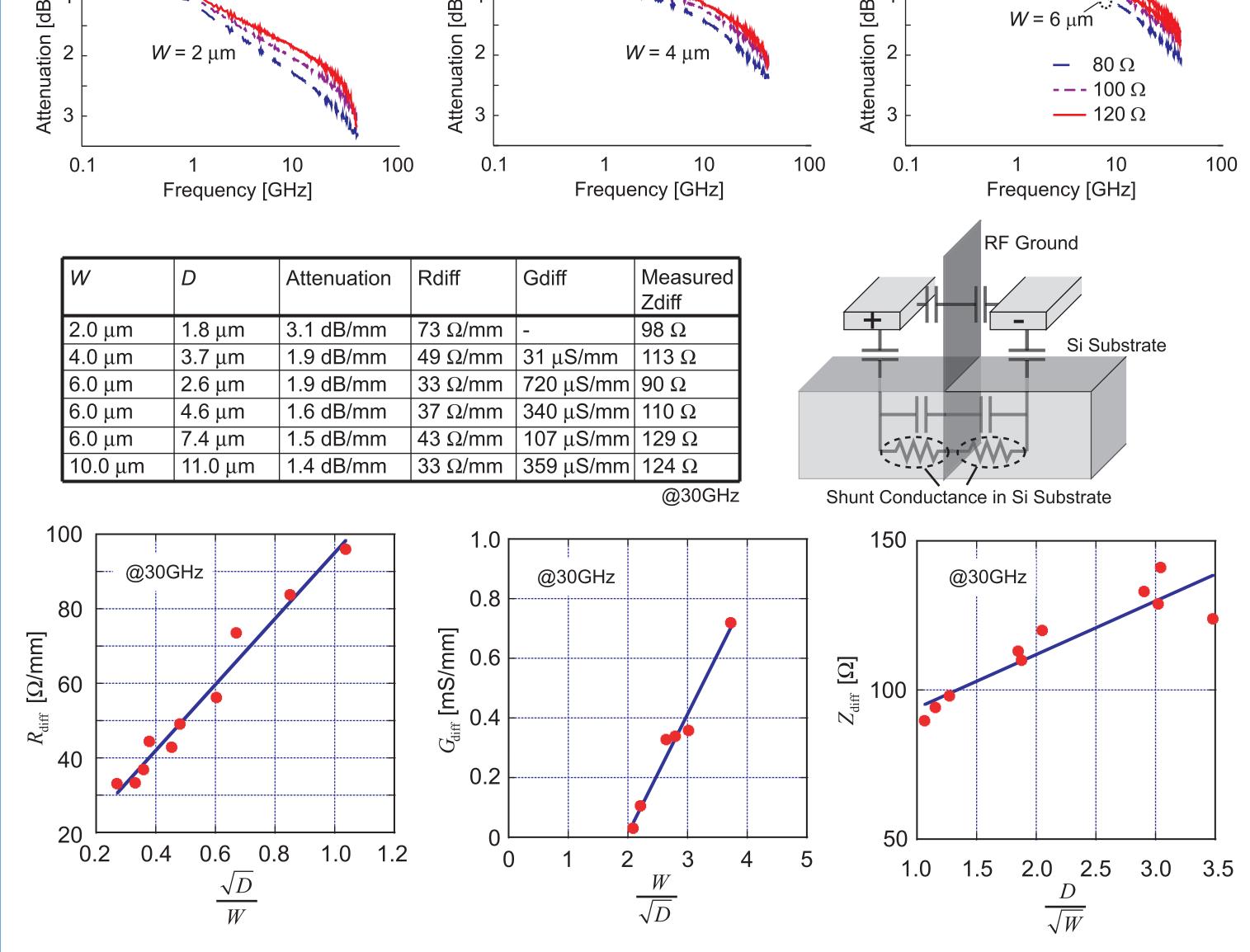

Empirical relationships found  $R_{

m diff} \propto rac{\sqrt{D}}{W}, \quad G_{

m diff} \propto rac{W}{\sqrt{D}}, \quad Z_{

m diff} \propto rac{D}{\sqrt{W}} \qquad \qquad \alpha \simeq rac{1}{2} \left(rac{R_{

m diff}}{Z_{

m diff}} + G_{

m diff} Z_{

m diff}

ight)$

Attenuation constant:

Attenuation characteristics depend on the WD product.

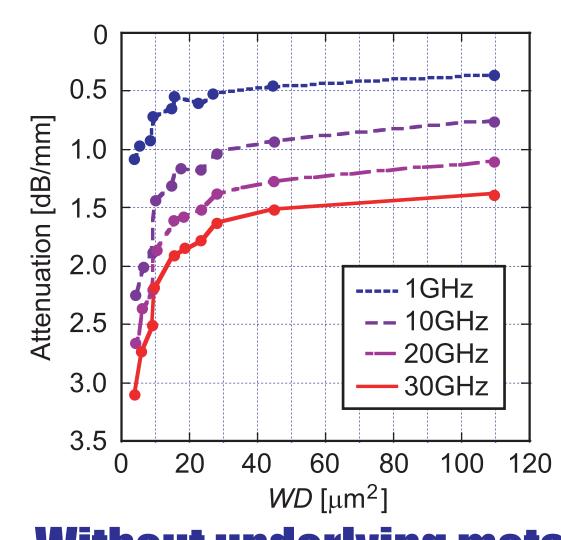

Without underlying metal

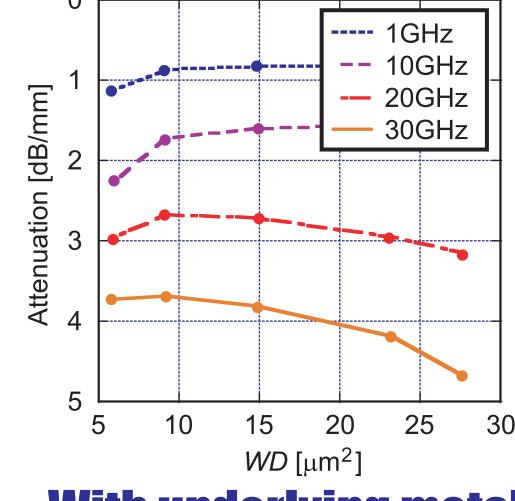

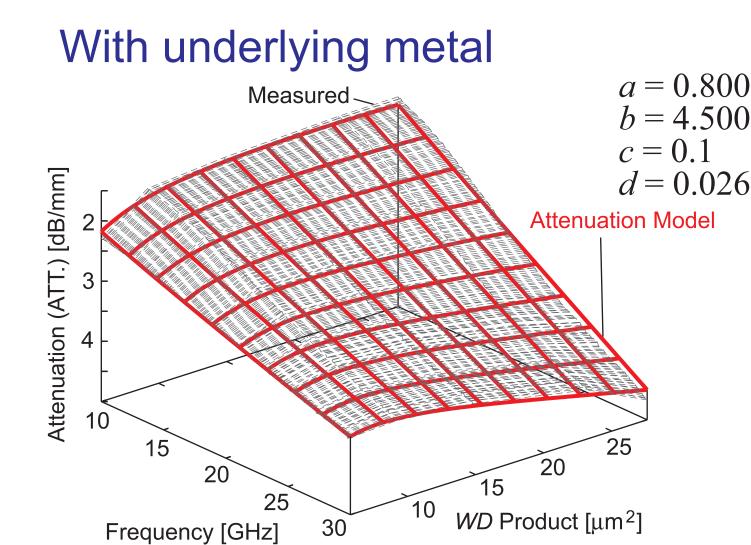

With underlying metal

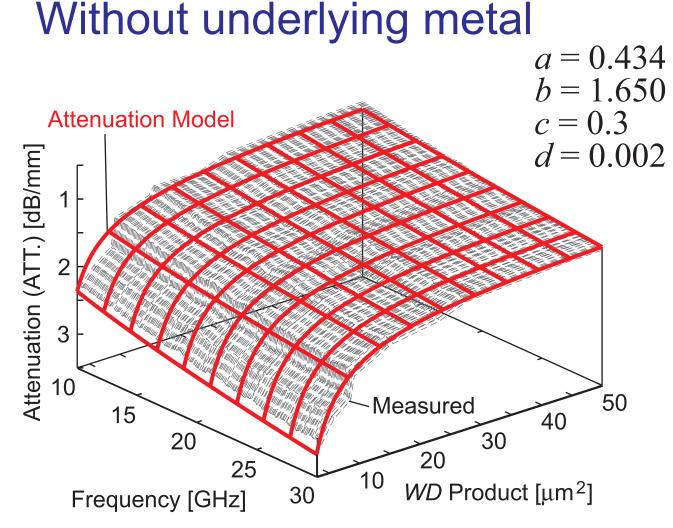

### Attenuation model

Attenuation ATT. can be characterized by a simple function of WD [µm<sup>2</sup>] and frequency f [GHz].

$ATT. = a + \frac{bf^c}{\sqrt{WD}} + df\sqrt{WD}$ Dielectric Loss Loss

# Conclusions

(This Study)

We can design on-chip transmission lines!!