## A 6.5-mW 5-Gbps On-Chip DTL Interconnect with a Low-Latency Asymmetric Tx in a 180nm CMOS Technology Takahiro Ishii, Hiroyuki Ito, Makoto Kimura, Kenichi Okada, and Kazuya Masu

Integrated Research Institute, Tokyo Institute of Technology, Japan

## Background

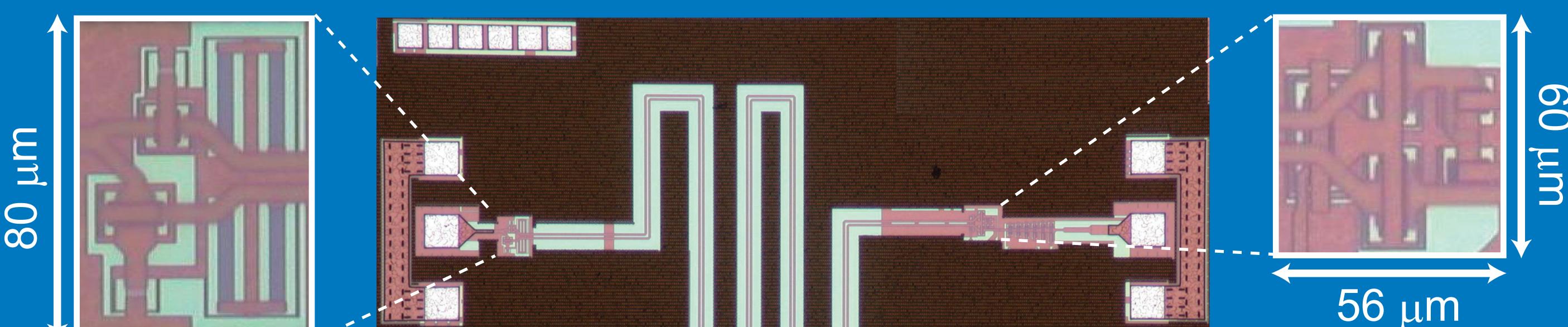

60 µm

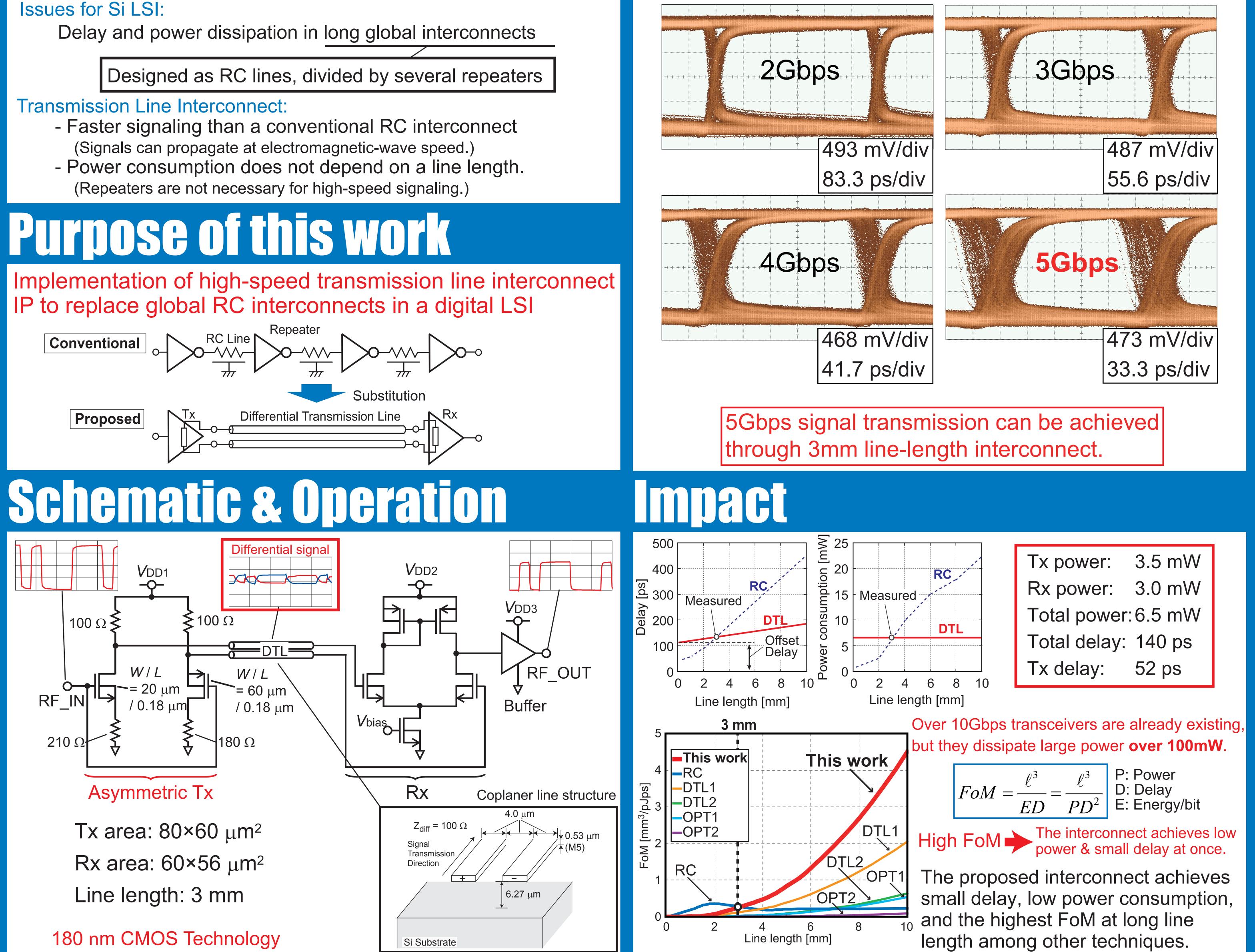

# Measured eve patterns

## HONG USION

Maximum 5 Gbps signaling can be achieved using the proposed circuit fabricated by 180 nm COMS technology.

The proposed interconnect has smaller delay and lower power consumption than the conventional RC interconnect over 3 mm.