# 1D-2 LVDS-type On-Chip Transmission Line Interconnect with Passive Equalizers in 90 nm CMOS Process Akiko Mineyama<sup>1</sup>, Hiroyuki Ito<sup>2</sup>, Takahiro Ishii<sup>1</sup>, Kenichi Okada<sup>1</sup>, and Kazuya Masu<sup>1</sup> <sup>1</sup>Integrated Research Institute, Tokyo Institute of Technology, Japan <sup>2</sup>Precision and Intelligence Laboratory, Tokyo Institute of Technology, Japan

## Background

Miniaturization of Si CMOS

Increase in global interconnect delays has complicated timing designs and has limited performances of LSI

Transmission line interconnects[1]

Much smaller delay than conventional lines High power-efficiencies at high-speed signaling

Purpose of this work-

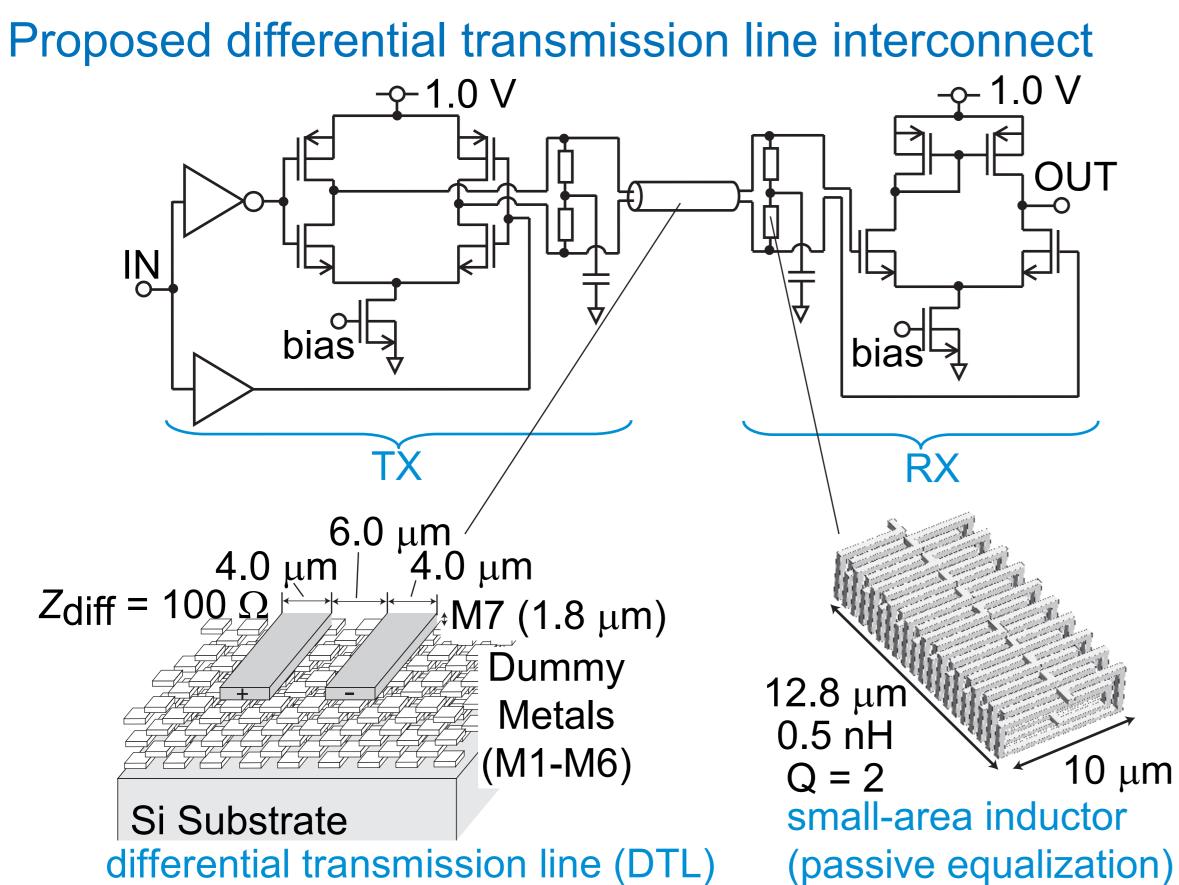

To propose a low-voltage-differential-signaling (LVDS) -type transmission line interconnect for achieving higher speed and higher power-efficiency

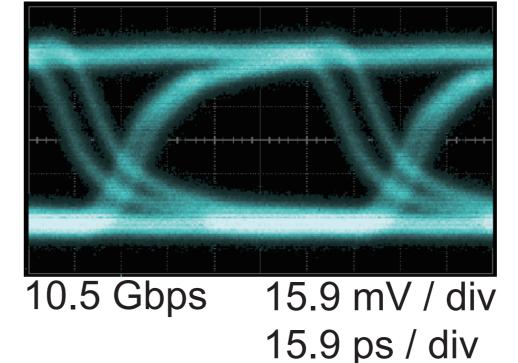

### Measurement results

### Performance summary

| Process | 90 nm standard Si CMOS |

|---------|------------------------|

|         |                        |

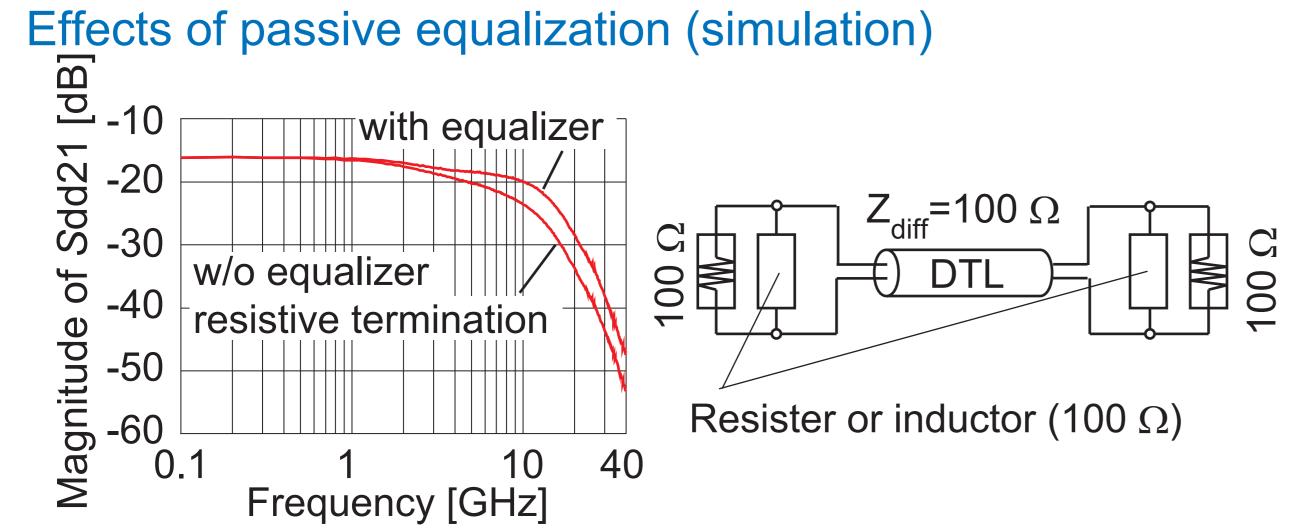

### Transmission line interconnect

| Maximum frequency         | 10.5 Gbps                 |

|---------------------------|---------------------------|

| Average delay of 23 chips | 173 ps / 5 mm             |

| Power consumption         | TX : 1.9 mW , RX : 0.8 mW |

| (VDD = 1V, 10Gbps)        | Total : 2.7 mW            |

| Energy per Bit            | 0.25 pJ / bit             |

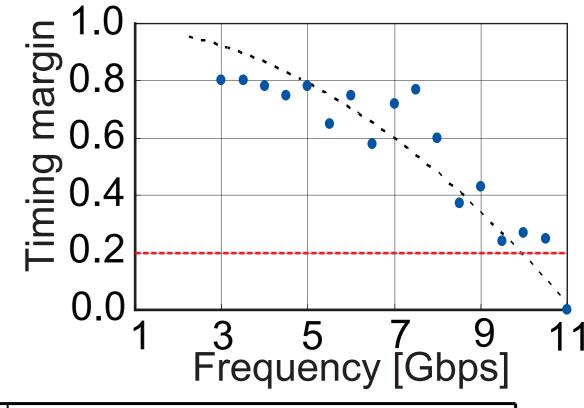

\* Eye-width margin is assumed to be over 20% of period at BER of  $10^{-12}$ .

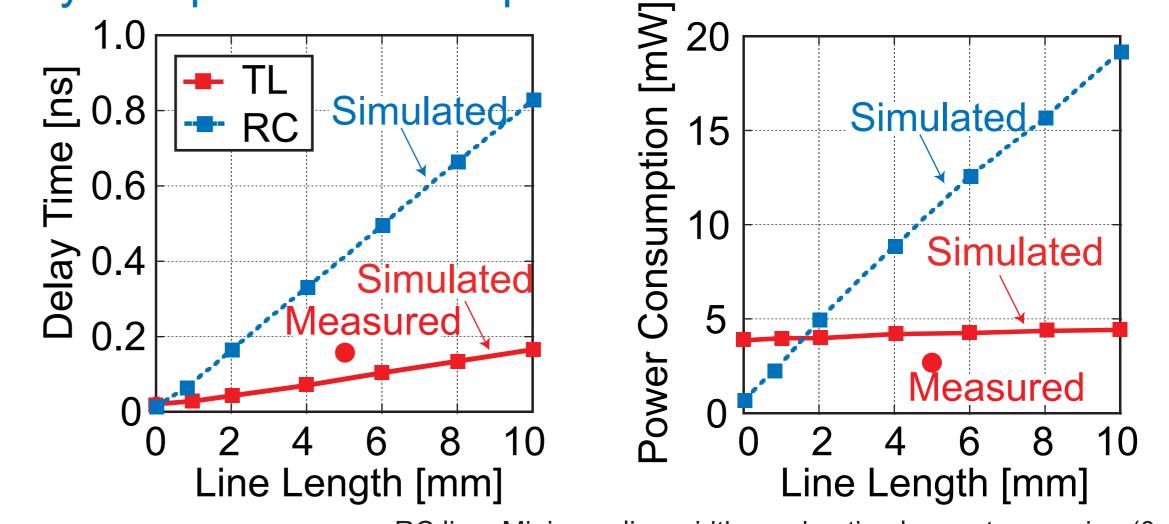

#### Delay and power consumption

RC line: Minimum line widths and optimal repeater spacing (0.4mm)

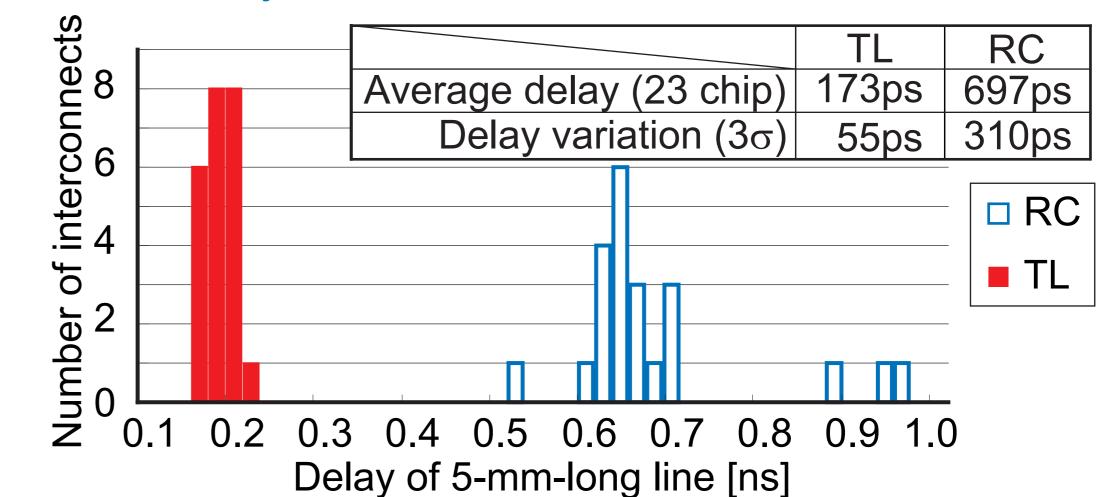

#### Measured delay variation

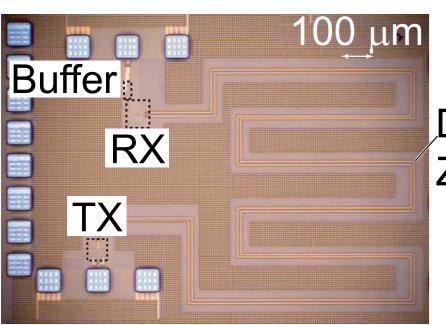

DTL (5 mm)  $Zdiff = 100 \Omega$

90 nm CMOS process Total area of TX and RX is11,100  $\mu$ m<sup>2</sup>

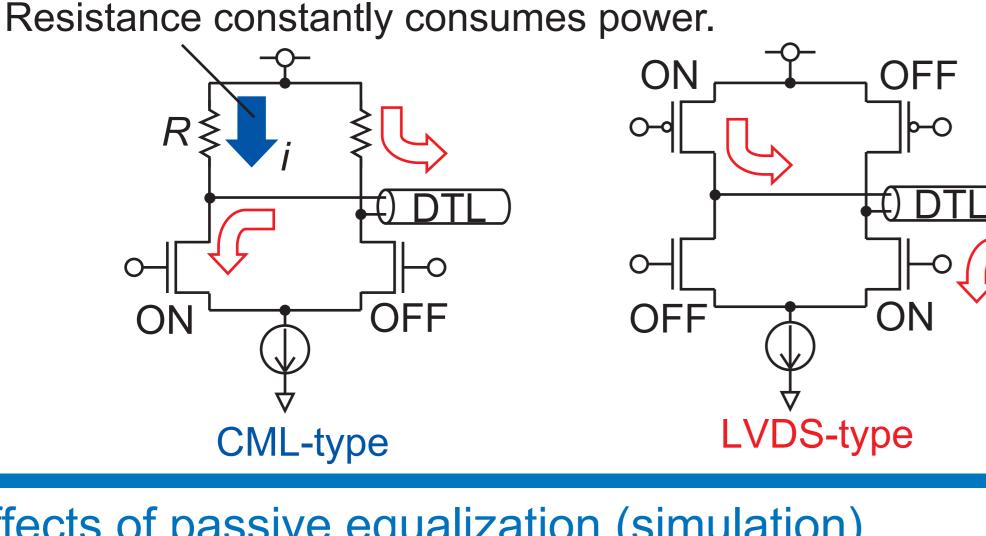

#### **Current flows**

## Conclusion

#### The LVDS-type on-chip transmission line interconnect

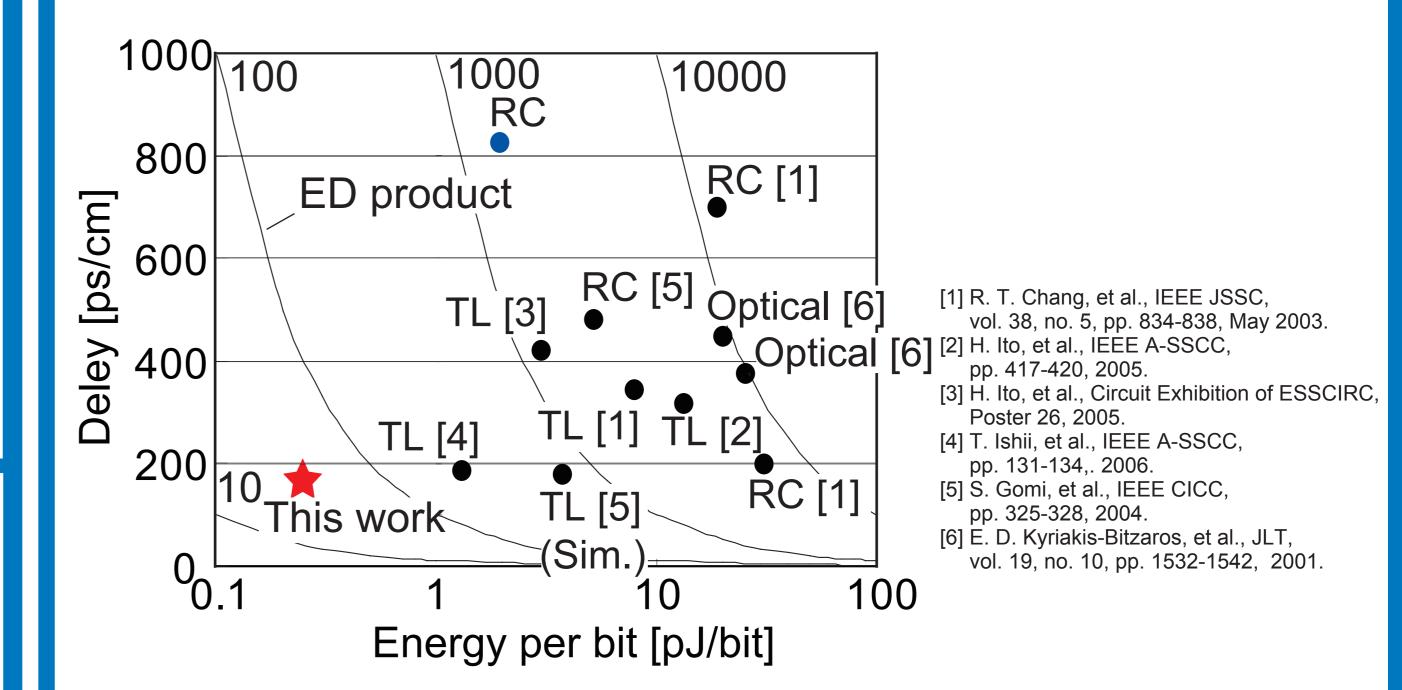

#### Delay of the proposed transmission line interconnect is among the shortest, and energy per bit is the best in reported on-chip long-interconnects.