## A Low-Power Differential Transmission Line Interconnect using Wafer Level Package Technology Tomoaki Maekawa<sup>1</sup>, Takahiro Ishii<sup>1</sup>, Junki Seita<sup>1</sup>, Hiroyuki Ito<sup>2</sup>, Kenichi Okada<sup>1</sup>, Hideki Hatakeyama<sup>3</sup>, Yusuke Uemichi<sup>3</sup>, Takuya Aizawa<sup>3</sup>, Tatsuya Ito<sup>3</sup>, Ryozo Yamauchi<sup>4</sup> and Kazuya Masu<sup>1</sup>

<sup>1</sup>Integrated Research Institute, Tokyo Institute of Technology, <sup>2</sup>Precision and Intelligence Laboratory, Tokyo Institute of Technology, <sup>3</sup>Electron Device Laboratory, Fujikura Ltd., <sup>4</sup>Fujikura Ltd., Japan

Signals are attenuated.

100 µ

Differential Transmission Line

# Background

### **Miniaturization of Si CMOS**

Increase of global interconnect delay

### Solution: **On-chip Transmission line interconnects[TLI]**[1-7] Advantages

# Challenge& Purpose

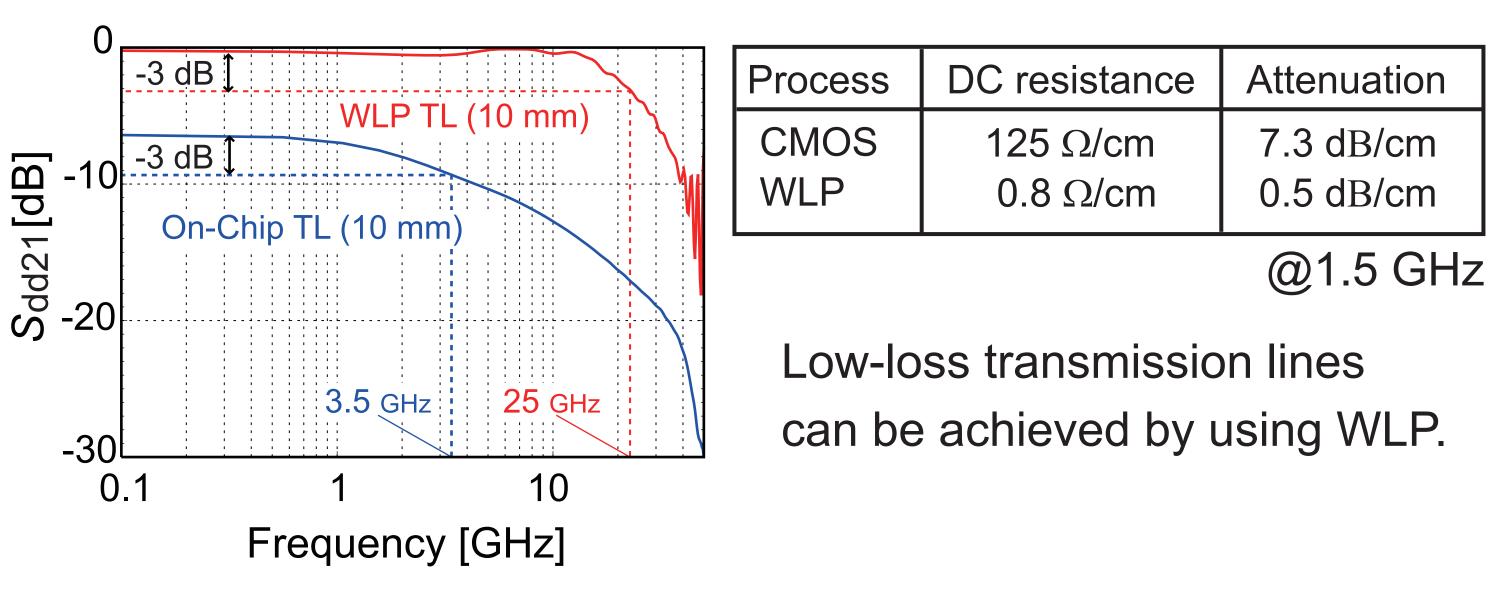

**Issue: Large attenuation due to large resistance of transmission lines** Power consumption of TLIs is almost determined by static power of a Tx and an Rx.

> Tx in conventional TLIs has to output largeamplitude signals for compensating large loss.

Rx in conventional TLIs need to have large gain for amplifying small input-signals.

Power of Tx will be saved if low-loss transmission line can be achieved.

Near-speed-of-light signaling Repeater less : low power consumption

[1]R.T.chang, et al., JSSC, 2006. [2]H.Ito, et al., IEDM 2004. [3]S.Gomi, et al., CICC, 2004. [4]H.Ito, et al., ASSCC, 2005.[5]T.Ishii, et al., ASSCC, 2006. [6]H.Ito, et al., IITC, 2007. [7]H.Ito, et al., VLSI, 2007.

# Mafer Level Package (MLP)

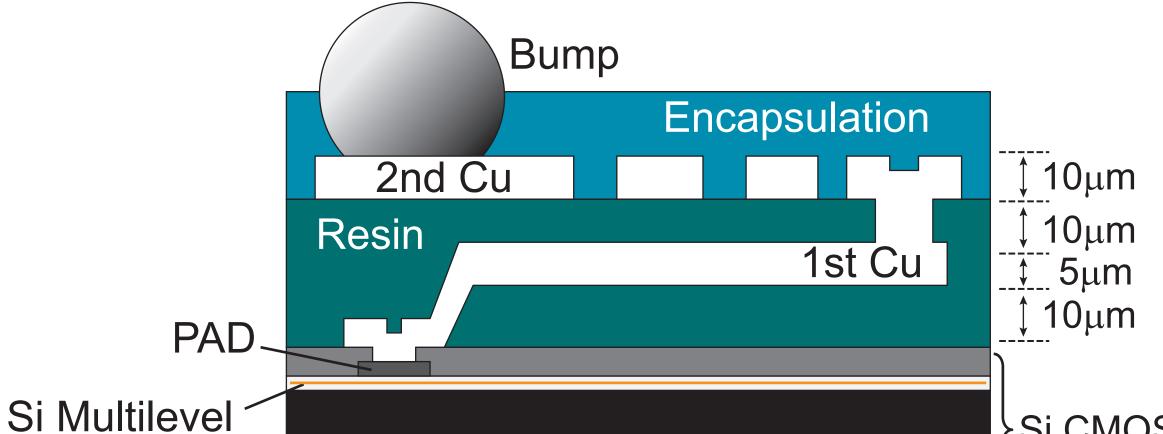

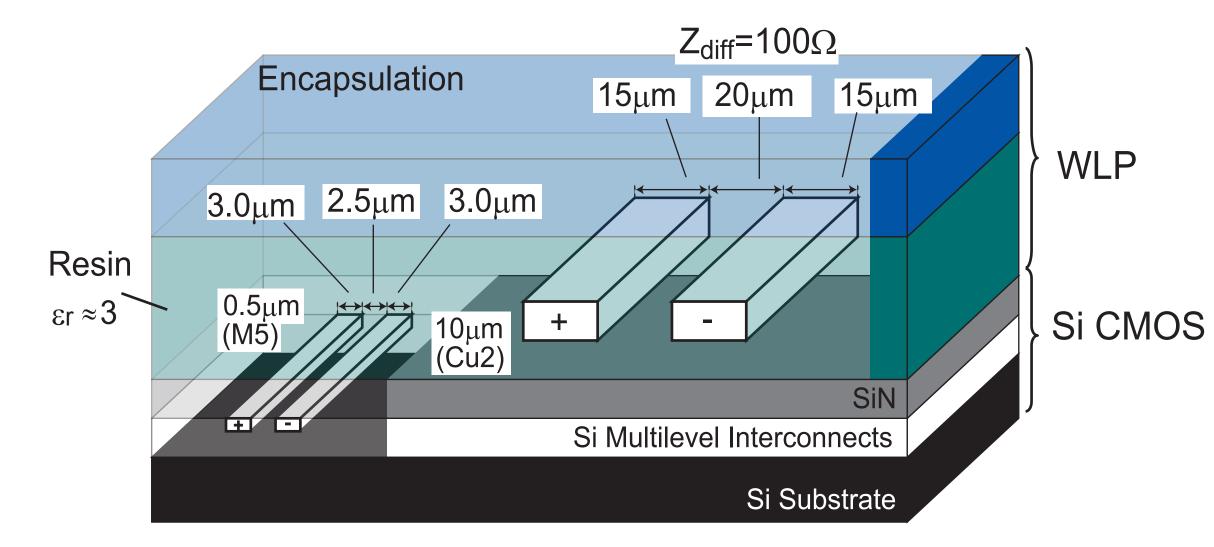

### Wafer Level Package Technology

Low resistive lines due to thick metal layers.

Si Substrate

Induced eddy currents in a Si substrate can be reduced because thick resin layers separate metal layers from a lossy Si substrate.

## **Purpose**

# To develop low-power TLIs with low-loss transmission lines in wafer level package process.

# Measurement Results

Rx

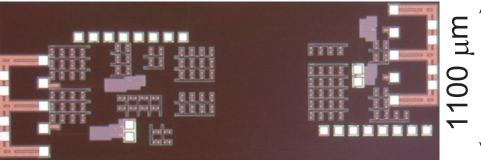

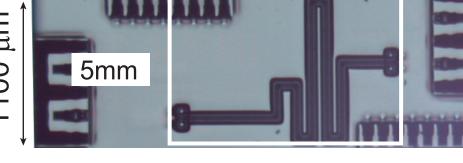

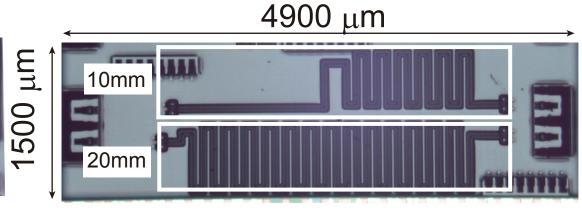

### Chip micrographs (0.18 $\mu$ m CMOS process)

3000 µm

10- and 20-mm-long TLI using WLP

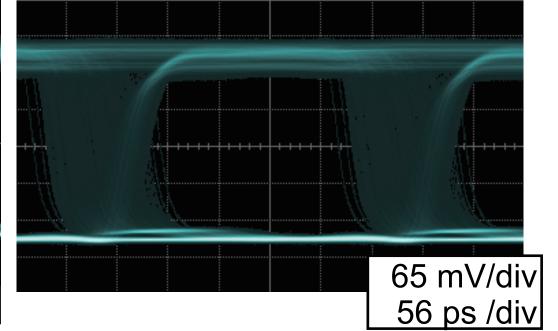

5-mm-long TLI using WLP The conventional TLI(reference) **Eye** patterns reference(2.5Gbps)

#### WLP5mm(2.5Gbps)

65 mV/div

56 ps /div

WLP20mm(2.5Gbps)

Si CMOS

o Tx

### **Structures of transmission lines**

Interconnects

### **Comparison of measured signal attenuation**

#### **Performance summary** • 5-mm-long TLIs

#### 0.18µm Si CMOS 0.18µm Si CMOS Technology 180 ps 178 ps Delay[Sim.] Tx: 4.1 mW(1. Tx : 6.5 mW(1.2 V) Power Consumption Rx : 3.1 mW(1.8 V) Rx: 1.3 mW(1 @3Gbps total : 5.5 m total: 9.5 mW Tx : 85 × 120 Tx : 90 × 140 μm<sup>2</sup> Area Rx : 80 × 50 μm<sup>2</sup> Rx : 80 × 50 Maximum 4.5 Gbps 3.5 Gbps bit rate Maximum bit rate is determined by eye-width. Eye-width margin is assumed to be over 20 % of period at BER

65 mV/div

56 ps /div

#### 10- and 20-mm-long WLP TLIs

| S WLP                                              | Line length                       | 10 mm                                                      | 20 mm                                                      |

|----------------------------------------------------|-----------------------------------|------------------------------------------------------------|------------------------------------------------------------|

|                                                    | Technology                        | 0.18μm Si CMOS WLP                                         |                                                            |

| .2 V)                                              | Delay[Sim.]                       | 232 ps                                                     | 350 ps                                                     |

| I.8 V)<br>nW<br>μm <sup>2</sup><br>μm <sup>2</sup> | Power<br>Consumption<br>@2.5 Gbps | Tx : 4.0 mW(1.2 V)<br>Rx : 1.2 mW(1.8 V)<br>total : 5.2 mW | Tx : 4.1 mW(1.2 V)<br>Rx : 1.4 mW(1.8 V)<br>total : 5.5 mW |

| S                                                  | Area                              | Tx : 85 × 120 μm²<br>Rx : 80 × 50 μm²                      | Tx : 85 × 120 μm²<br>Rx : 80 × 50 μm²                      |

| R of 10 <sup>-12</sup> .                           | Maximum<br>bit rate               | 2.6 Gbps                                                   | 3.4 Gbps                                                   |

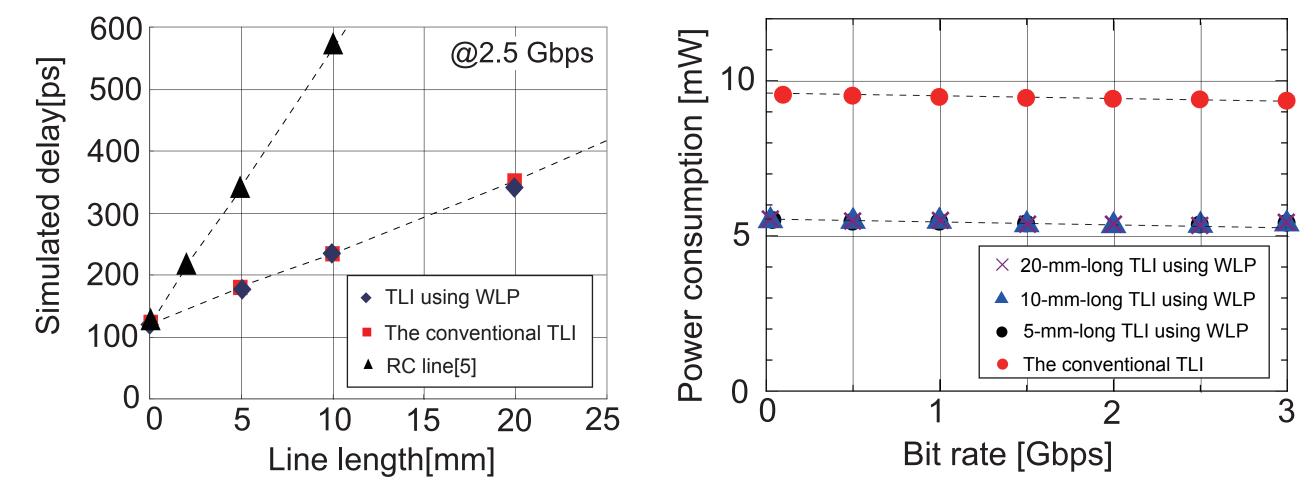

### **Discussions with delay and power consumption**

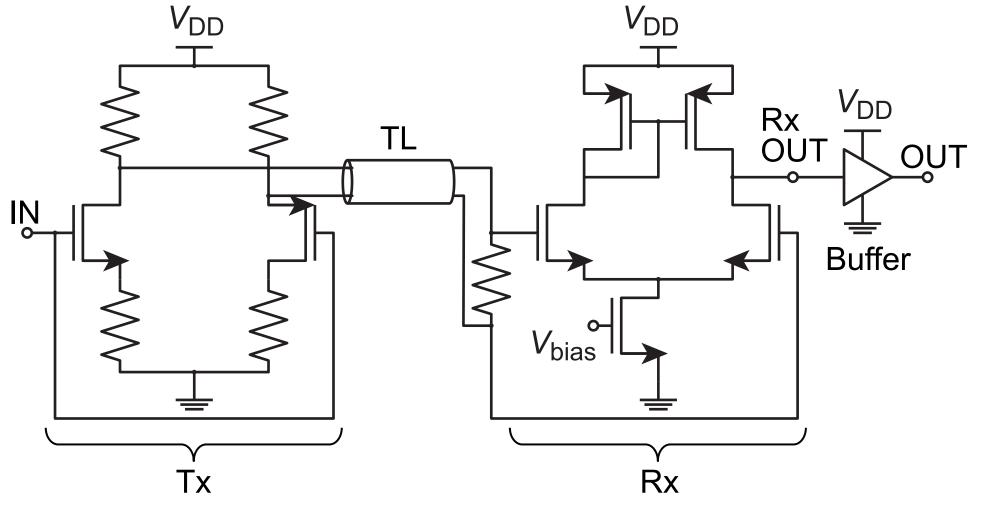

### Schematic of a TLI

Tx consists of a NMOS source degeneration and a PMOS source follower for generating differential signals [5].

- Simulated delay of TLIs using WLP linearly increase as line length increases.

- The proposed TLI has almost the same delay as the conventional TLI. Power of TLIs hardly depends on bit rates and line length. • TLIs using WLP achieve 42% smaller power than conventional TLIs.

# **Conclusions**

- A low power on-chip TLI using WLP technology is developed.

- Proposed TLIs using WLP had smaller power consumption than that using only CMOS process.

- Unique design strategies for on-chip TLIs using WLP would be required for achieving higher-speed signaling.