# 微細CMOSプロセスを用いたMEMS駆動用26V出力チャージポンプ回路

東京工業大学ソリューション研究機構

白根 篤史, 伊藤 浩之, 石原 昇, 益一哉

# 背景•目的

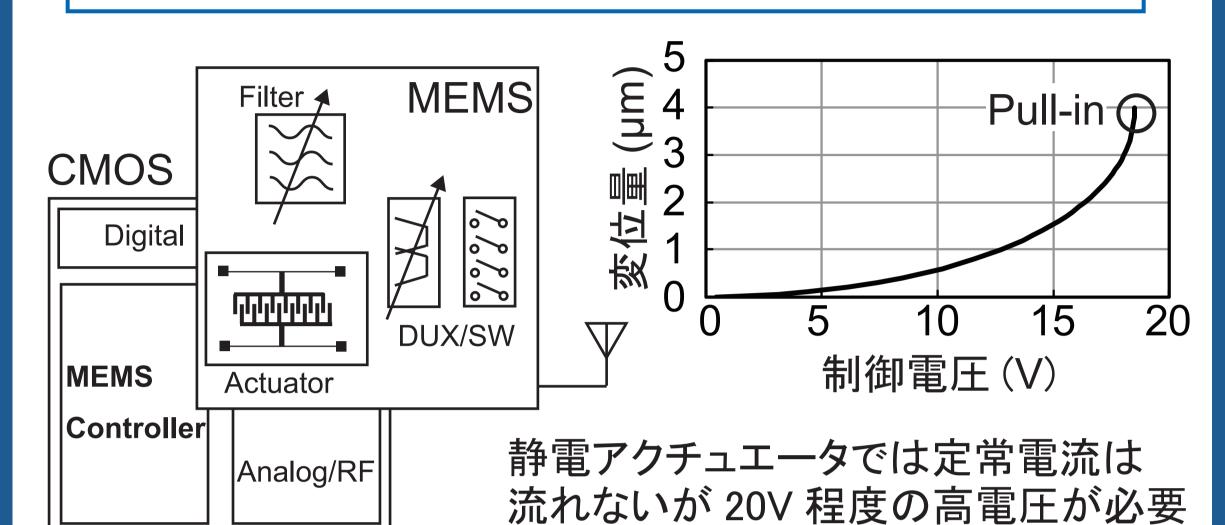

CMOS&MEMS の異種機能集積技術を用いた マルチバンド RFトランシーバの実現

微細 CMOS チャージポンプ回路の高出力電圧化

RF 回路との混載が可能

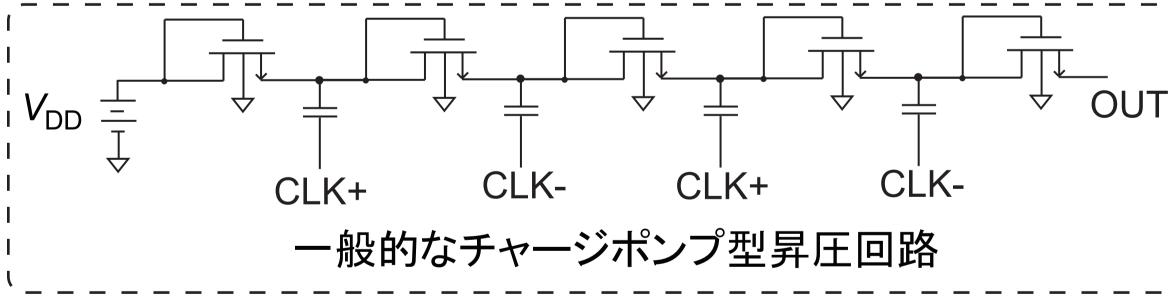

## チャージポンプ型昇圧回路の課題

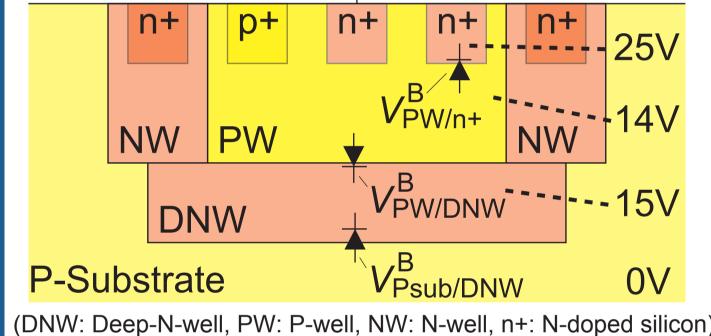

PN 接合のブレークダウン電圧及びキャパシタの 耐圧がチャージポンプ回路の最大出力電圧を律則

Psub/DNW

NW PW V<sub>PW/DNW</sub> DNW P-Substrate . NW: N-well. n+: N-doped silicon

1.0×10<sup>-3</sup>+

€<sub>1.0×10</sub>-5

1.0×10<sup>-6</sup>

び 1.0×10

1.0×10<sup>-8</sup>

1.0×10<sup>-4</sup> 180nm CMOS

実測値

PW/n+

Voltage between pn-junction (V)

上記の回路の出力電圧は 5×(V<sub>DD</sub>-V<sub>th</sub>) となる

NMOS 断面図 (with triple well)

デバイス耐圧 (180nm CMOS)

- MIM キャパシタ:5V

- PN 接合

- PW/n+ : 11V

- PW/DNW : 15V

- Psub/DNW: 15V

- 電源電圧は3.3V (IO 用 )

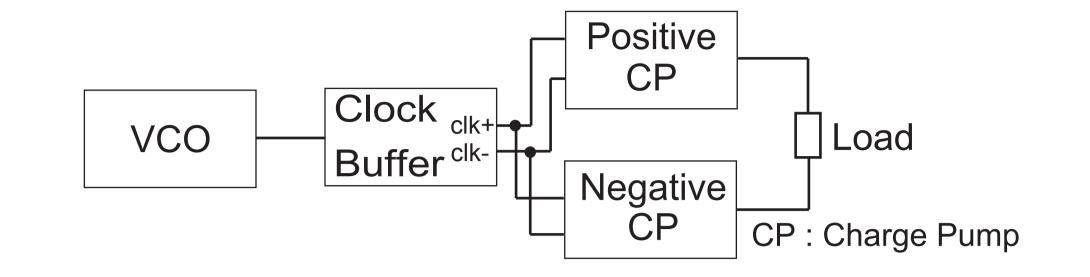

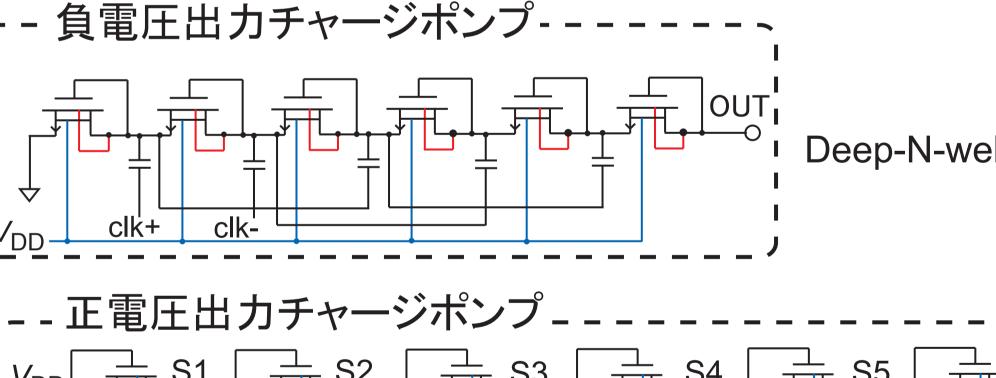

#### 提案チャージポンプ型昇圧回路

#### 高出力電圧化に向けた提案回路技術

- 正と負のチャージポンプ回路の利用により、ブレークダウン 電圧の2倍程度まで昇圧

- 各ウェルの適切なバイアス電圧の設定により、一つの ブレークダウン電圧を超えて昇圧

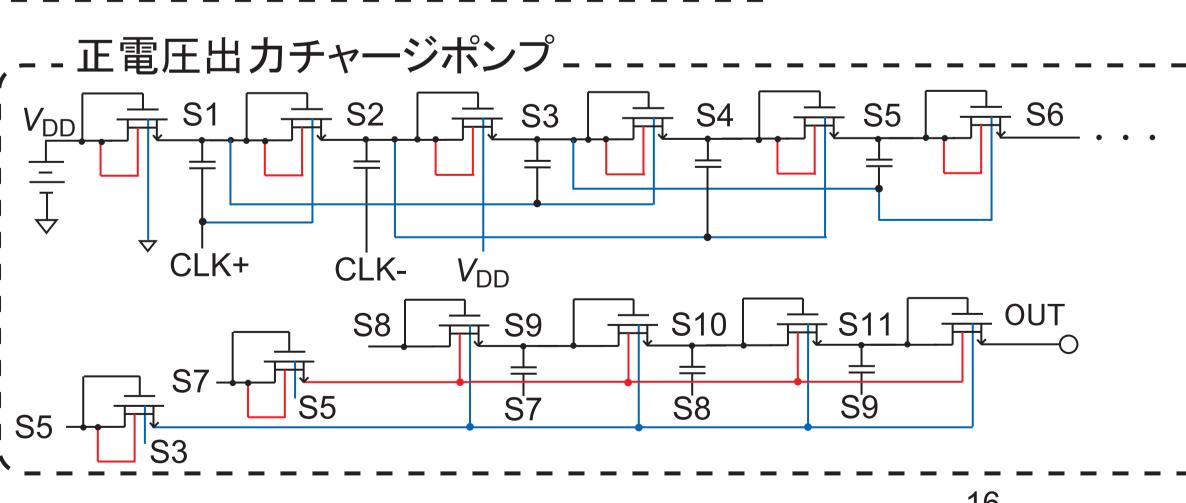

- クロック信号の新たな供給手法により、キャパシタにかかる 電圧を低減

- PN 接合を逆バイアスに保つ

- PN 接合のブレークダウン電圧 以下に保つ

- 二つの PN 接合における ブレークダウン電圧を利用

Time (µs)

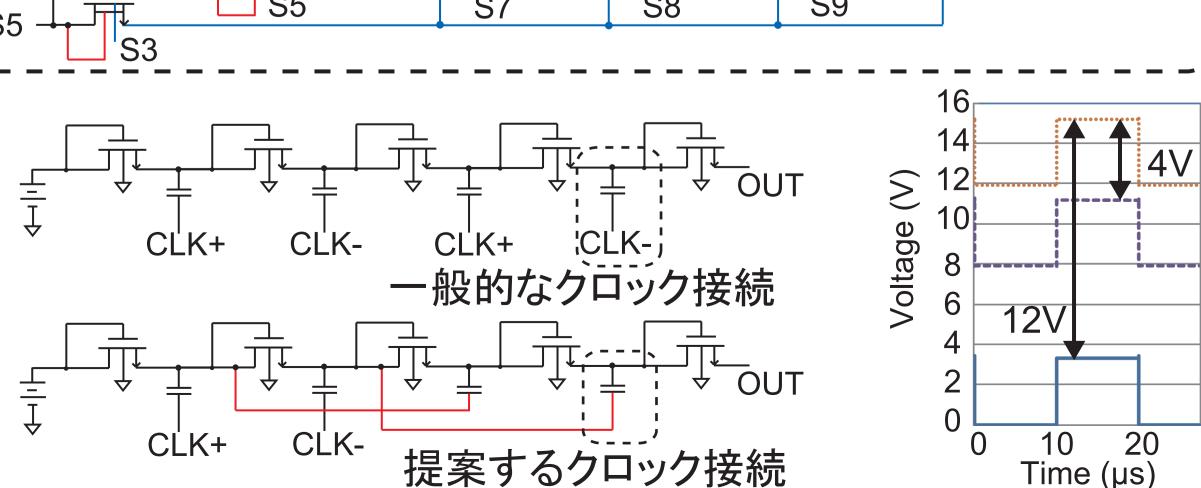

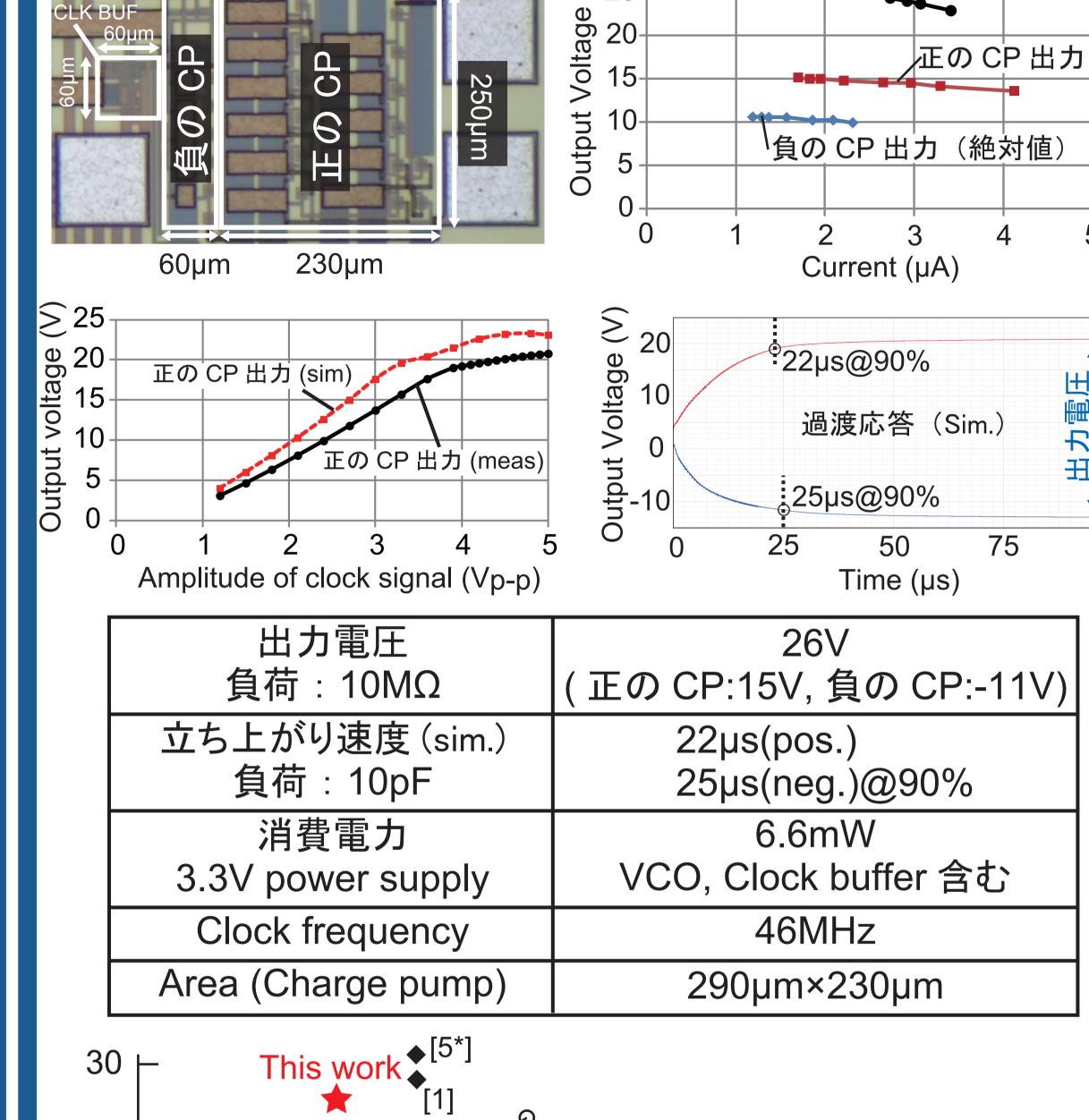

### 試作測定結果

180nm CMOS process

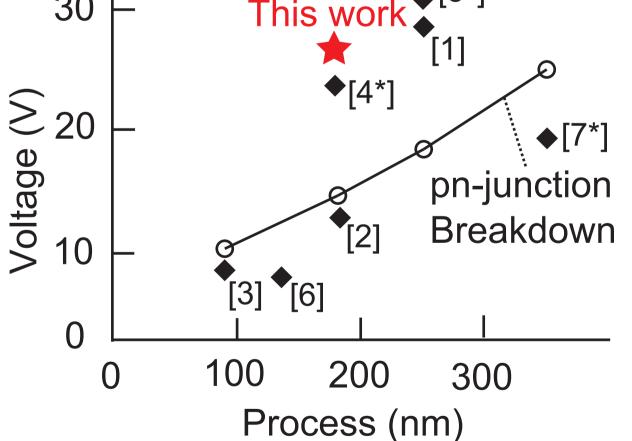

[1]ASSCC2005, M. Ker, et al. [2]ESSCIRC2003, M. Innocent, et al. [3]IEDM2010 R. Henderson, et al. [4]ESSCIRC2005 E. Racape, et al. (\*BV=30V)

/正と負の CP 出力

[5]CICC2006 M. Bouhamame, et al. (\*Bi-CMOS) [6]ISSCC2007 A. Richelli, et al.

[7]TCAS II 2006 M. Hoque, et al. (\*SOI)

#### まとめ

- 高出力電圧化に向けた3つの回路技術を提案

- 1. 正と負のチャージポンプ回路の利用

- 2. 各ウェルの適切なバイアス電圧の設定

- 3. クロック信号の新たな供給手法

- 180nm Si CMOS プロセスを用いて、設計試作、測定評価を 行い、回路の有効性を確認

- ブレークダウン電圧 11V,15V 及び、キャパシタ耐圧 5V において 出力電圧 26V を実現した